Hardware

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 771

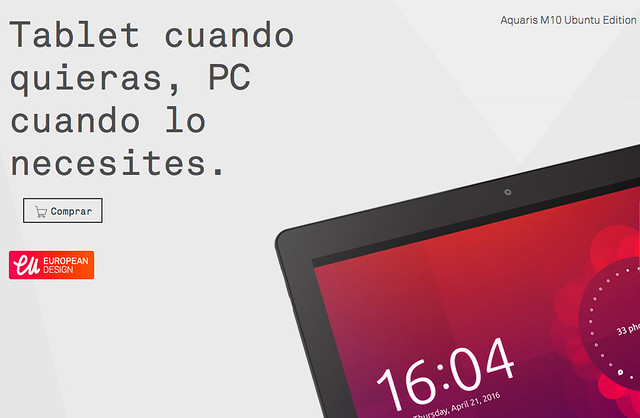

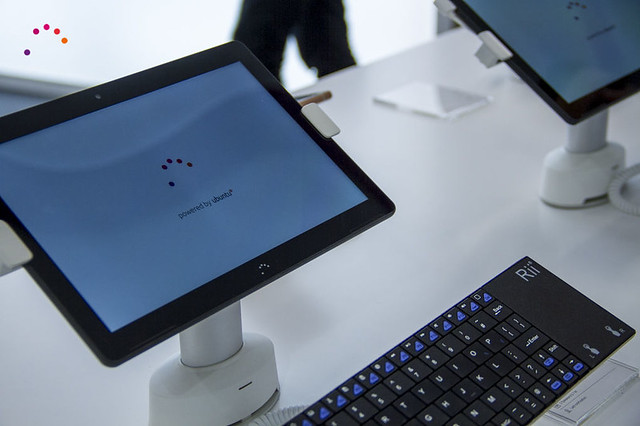

Canonical y la compañía BQ firmaron hace poco tiempo un acuerdo para lanzar la primera tableta híbrida con soporte dual de interfaces, tanto móvil como de escritorio. Hablamos de la BQ Aquaris M10 Ubuntu Edition , una tableta que desde hace poco tiempo se encuentra ya disponible para reservar. Sin embargo, si sois unos usuarios algo más exigentes y buscáis un equipo más potente, la compañía MJ parece tener la respuesta a vuestra demanda.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 676

Desde hace unos días ya se puede reservar la compra de la Aquaris M10 Ubuntu Edition, la primera tablet que integra el sistema de Canonical y que nos llega de la mano de uno de sus socios habituales, la compañía española BQ.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 1290

¡Oye! ¿Qué vas a haser con eso si no lo usas? ¡Súbelo súbelo! Ya sé ya sé, llevo una semana desaparecido. Cosas de las vacaciones, pero ya he vuelto. Digamos que tras algunos e-mails preguntándome sobre tarjetas Ethernet no me he podido contener de explicar la tarjeta que yo uso: Arduino Yún.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 956

Hoy es día 28 de marzo, ¿Sabéis lo que significa? Que ya está disponible para su reserva la primera tablet convergente de Ubuntu: la BQ Aquaris M10 Ubuntu Edition. Se puede reservar desde la página web oficial de BQ y está disponible en dos versiones: la versión HD por un precio de 249.90€ y la versión FHD por 289.90€. ¿Qué diferencia hay entre los dos modelos? Sólo la pantalla: la versión FHD tiene una pantalla con resolución FHD 1920 x 1200 – 240 ppi, mientras que la HD tiene una pantalla de HD 1280 x 800 – 160 ppi, lo que se notará por ofrecer menos detalles.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 723

Desde hoy se puede reservar la primera tablet Ubuntu de la historia, la Aquaris M10 Ubuntu Edition de Bq. Como ya comentamos en su día, utilizará Ubuntu Touch con soporte legacy para ejecutar algunas aplicaciones de escritorio como Firefox y LibreOffice. Además será el primer dispositivo en ofrecer una experiencia realmente convergente con el sistema operativo de Canonical.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 623

Durante el día de ayer, BQ y Canonical han lanzado la fecha de venta y la disponibilidad de la nueva BQ Aquaris M10 Ubuntu Edition. Esta nueva tablet con el sobrenombre de Freezer, se podrá reservar a partir del 28 de marzo. Los que lo hagan recibirán la tablet durante el mes de abril cuando de comercialice de manera normal. Desgraciadamente hasta el próximo día 28 de marzo no sabremos ni conoceremos los precios de esta nueva tablet con Ubuntu Phone.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 833

El pasado 22 de febrero se presentó la bq Aquaris M10 Ubuntu Edition que como sabes es la primera tablet con Ubuntu, además del primer dispositivo que nos ofrece la tan esperada convergencia entre un dispositivo móvil y el entorno de PC.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 734

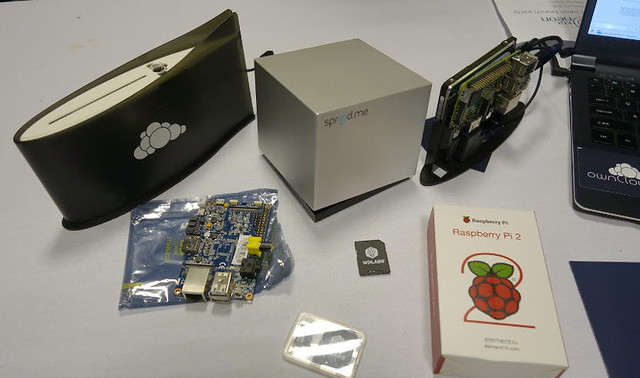

Hace tiempo que conocimos las intenciones de los desarrolladores de OwnCloud de crear un dispositivo que permita a sus usuarios tener una nube en casa sin tener que pagar por un gran servidor. Al final y tras varias alianzas lo han conseguido y dentro de poco se lanzará al mercado OwnCloud Pi un dispositivo que ofrecerá las bondades del cloud con la potencia de Ubuntu.

- Detalles

- Escrito por: : La Redacción

- Categoría: Hardware

- Visitas: 631

En ownCloud están que no paran y tras lanzar la semana pasada ownCloud 9 anuncian ahora un experimento que suena… a producto redondo, sí, y ahora veréis por qué; aunque os lo podéis imaginar: tu propia nube, pero de verdad, asequible y accesible.